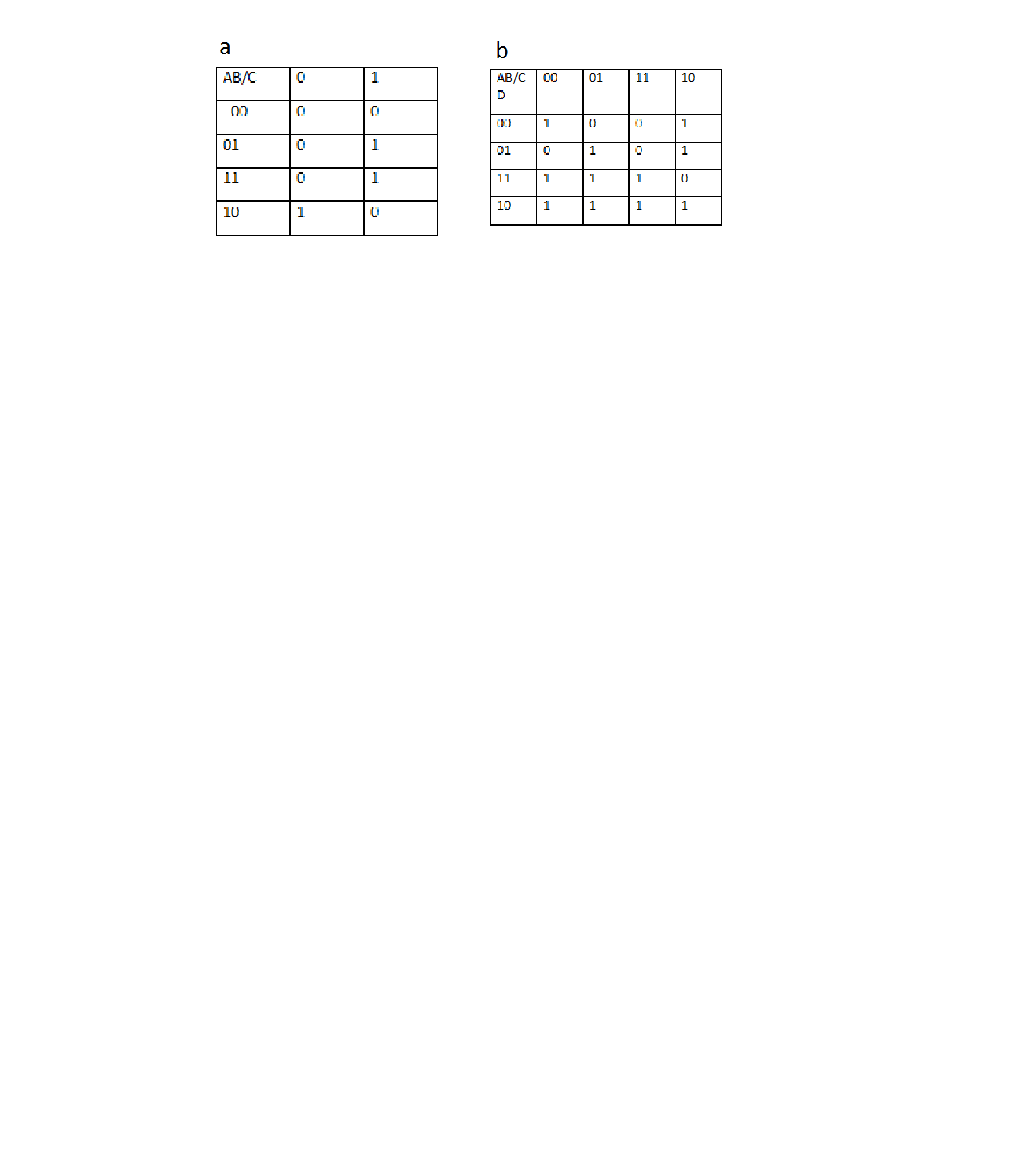

Part a) is for the left K-map, Part b) is for the right K-map.

a.

i)

SOP=A′BC+ABC+AB′C′

POS=(A′B′+C′)(A′B′+C)(A′B+C′)(AB+C′)(AB′+C)

(A′B′+C′)=(A′+C′)(B′+C′)=(A′+C′+B′)(A′+C′+B)×

×(B′+C′+A′)(B′+C′+A)=(A′+C′+B′)(A′+C′+B))(B′+C′+A)

(A′B′+C)=(A′+C)(B′+C)=(A′+C+B)(A′+C+B′)×

×(B′+C+A)(B′+C+A′)=(A′+C+B)(A′+C+B′)(B′+C+A)

(A′B+C′)=(A′+C′)(B+C′)=(A′+C′+B)(A′+C′+B′)×

×(B+C′+A)(B+C′+A′)=(A′+C′+B)(A′+C′+B′)(B+C′+A)

(AB+C′)=(A+C′)(B+C′)=(A+C′+B)(A+C′+B′)×

×(B+C′+A)(B+C′+A′)=(A+C′+B)(A+C′+B′)(B+C′+A′)

(AB′+C)=(A+C)(B′+C)=(A+C+B)(A+C+B′)×

×(B′+C+A)(B′+C+A′)=(A+C+B′)(A+C+B′)(B′+C+A′)

Standard form:

POS=(A′+C′+B′)(A′+C′+B))(B′+C′+A)(A′+C+B)(A′+C+B′)×

×(B′+C+A)(B+C′+A)

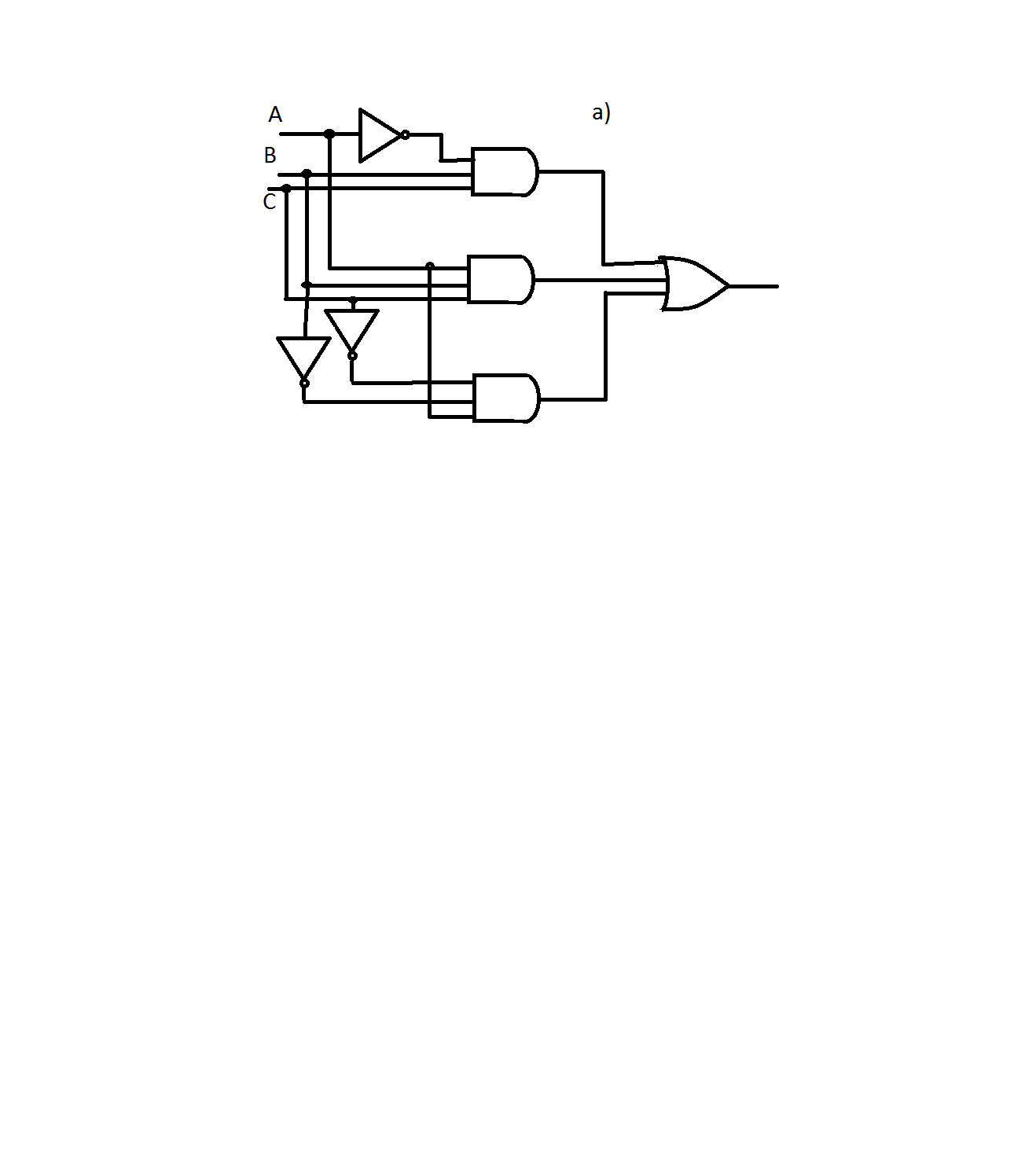

ii)

iii)

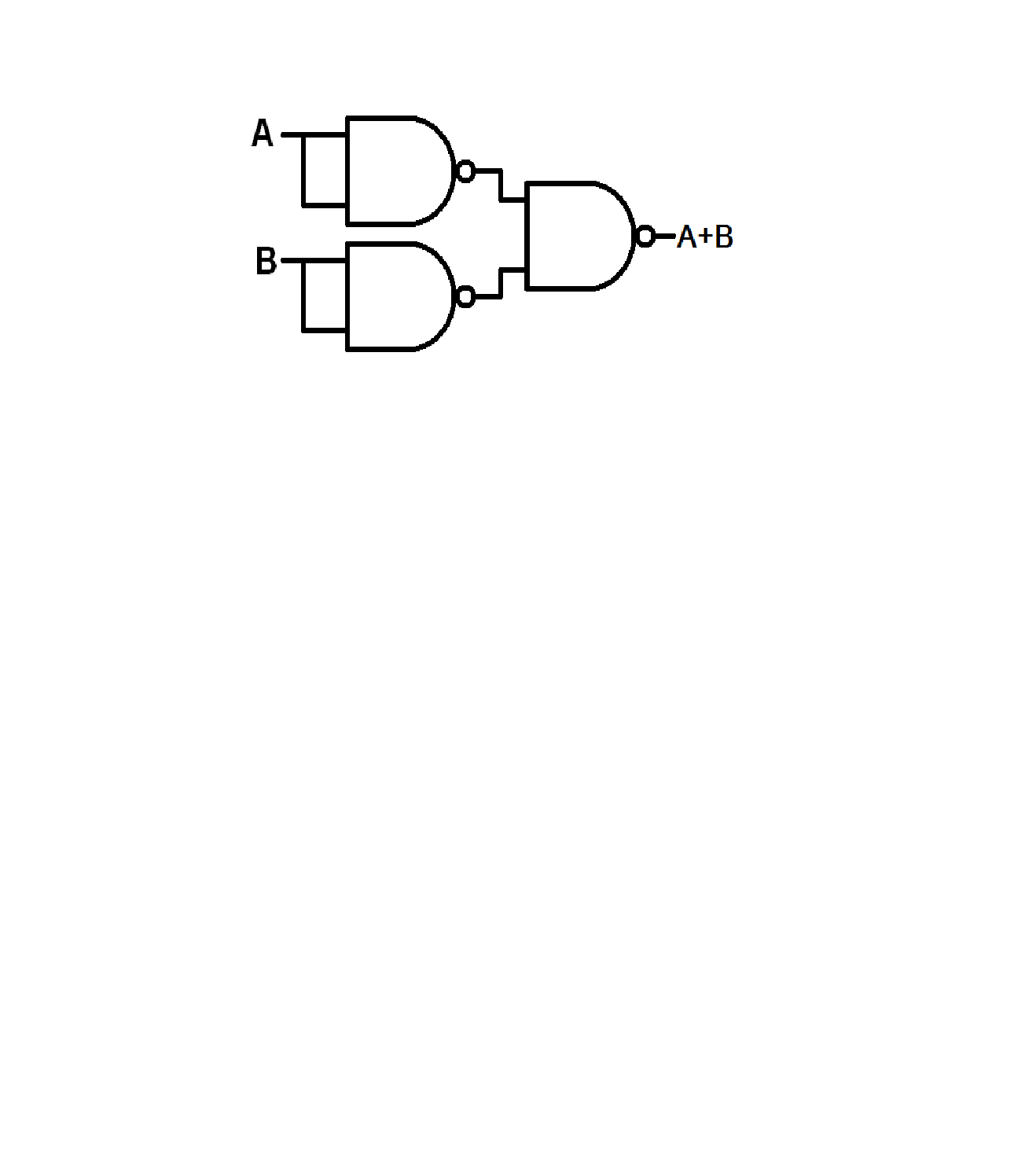

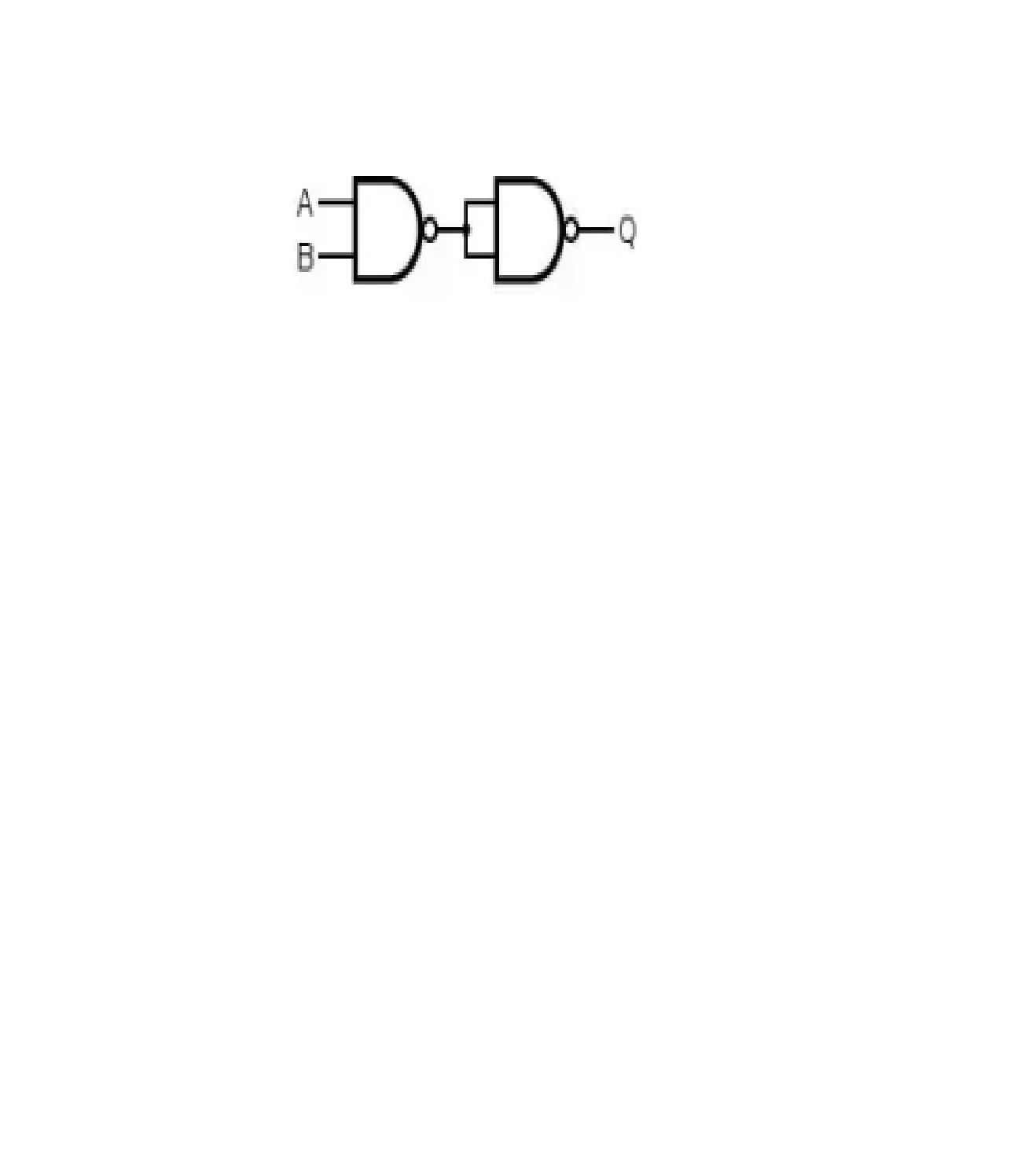

OR gate using NAND gate:

AND gate using NAND gate:

Then:

b)

I)

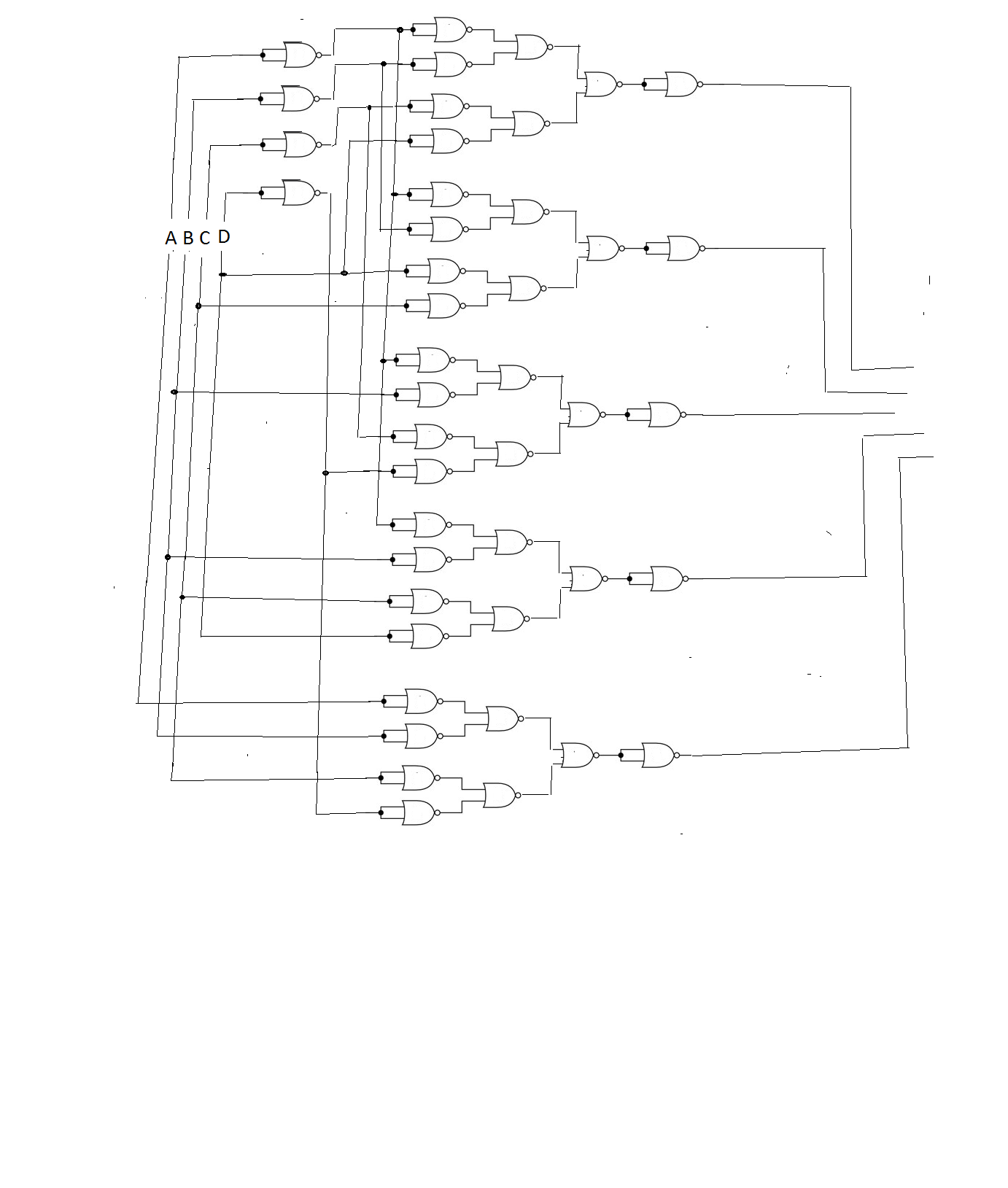

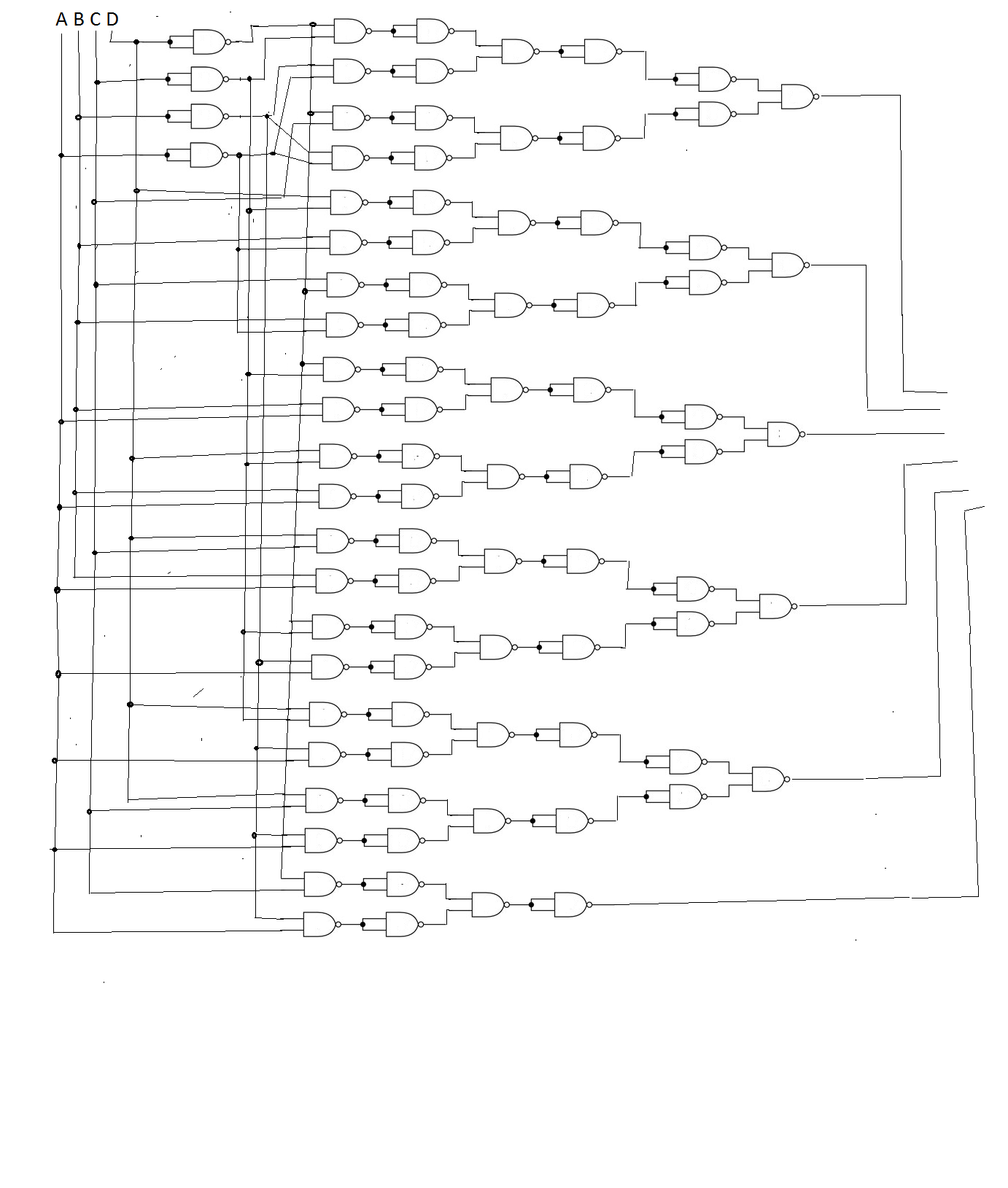

SOP=A′B′C′D′+A′B′CD′+A′BC′D+A′BCD′+ABC′D′+

+ABC′D+ABCD+AB′C′D′+AB′C′D+AB′CD+AB′CD′

POS=(A′B′+C′D)(A′B′+CD)(A′B+C′D′)(A′B+CD)(AB+CD′)

ii)

b)

iii)

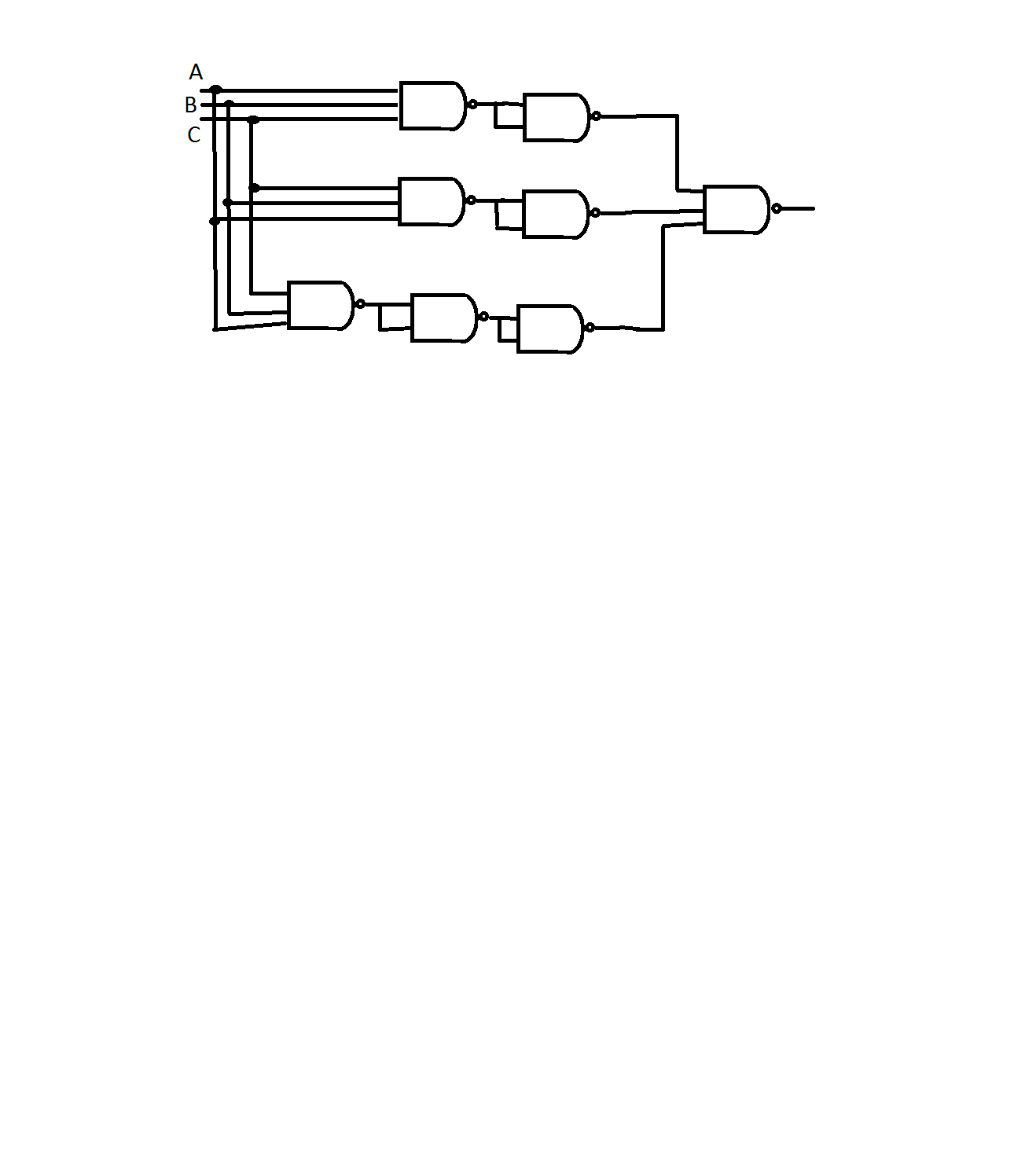

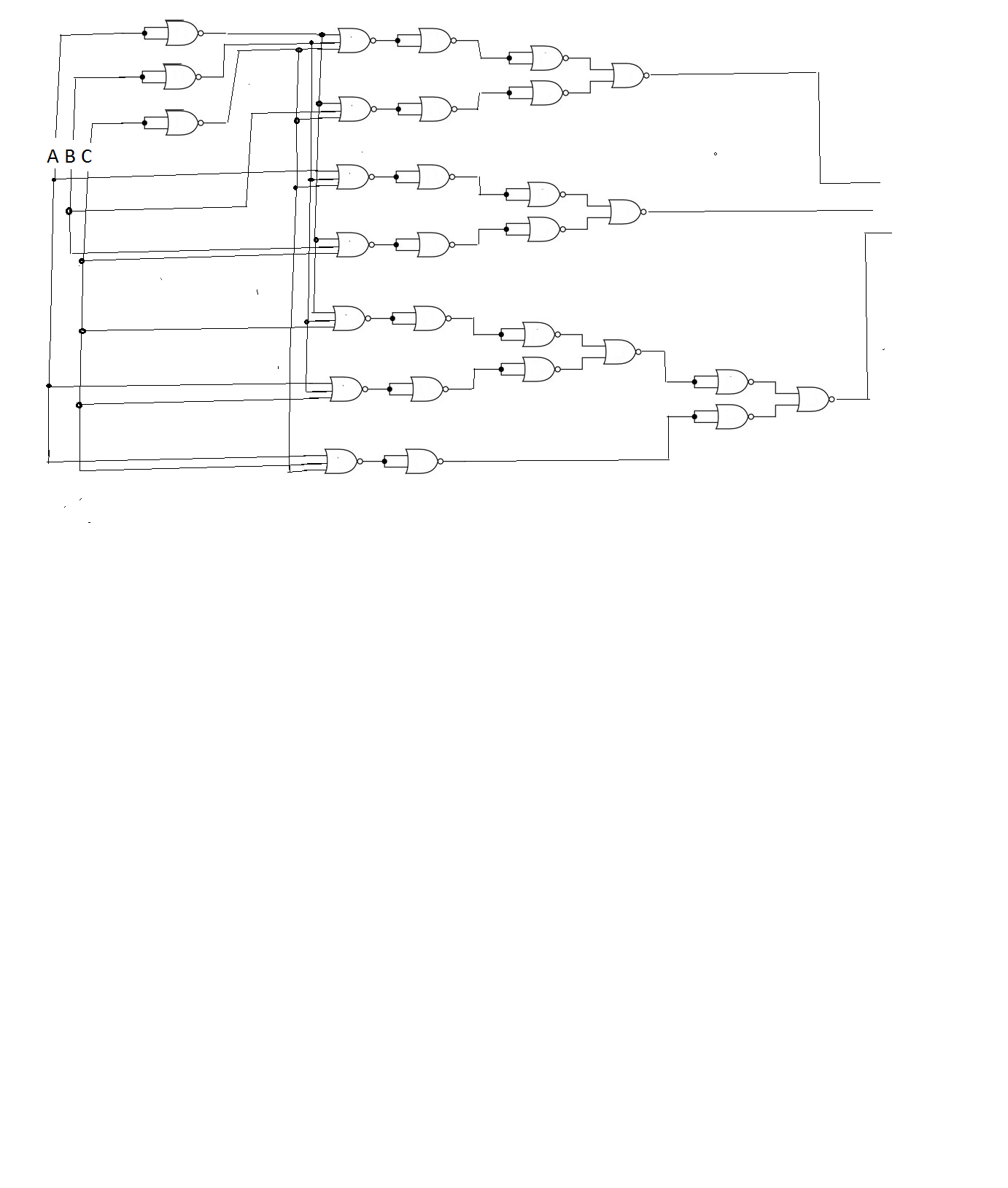

SOP using NAND gates:

iii)

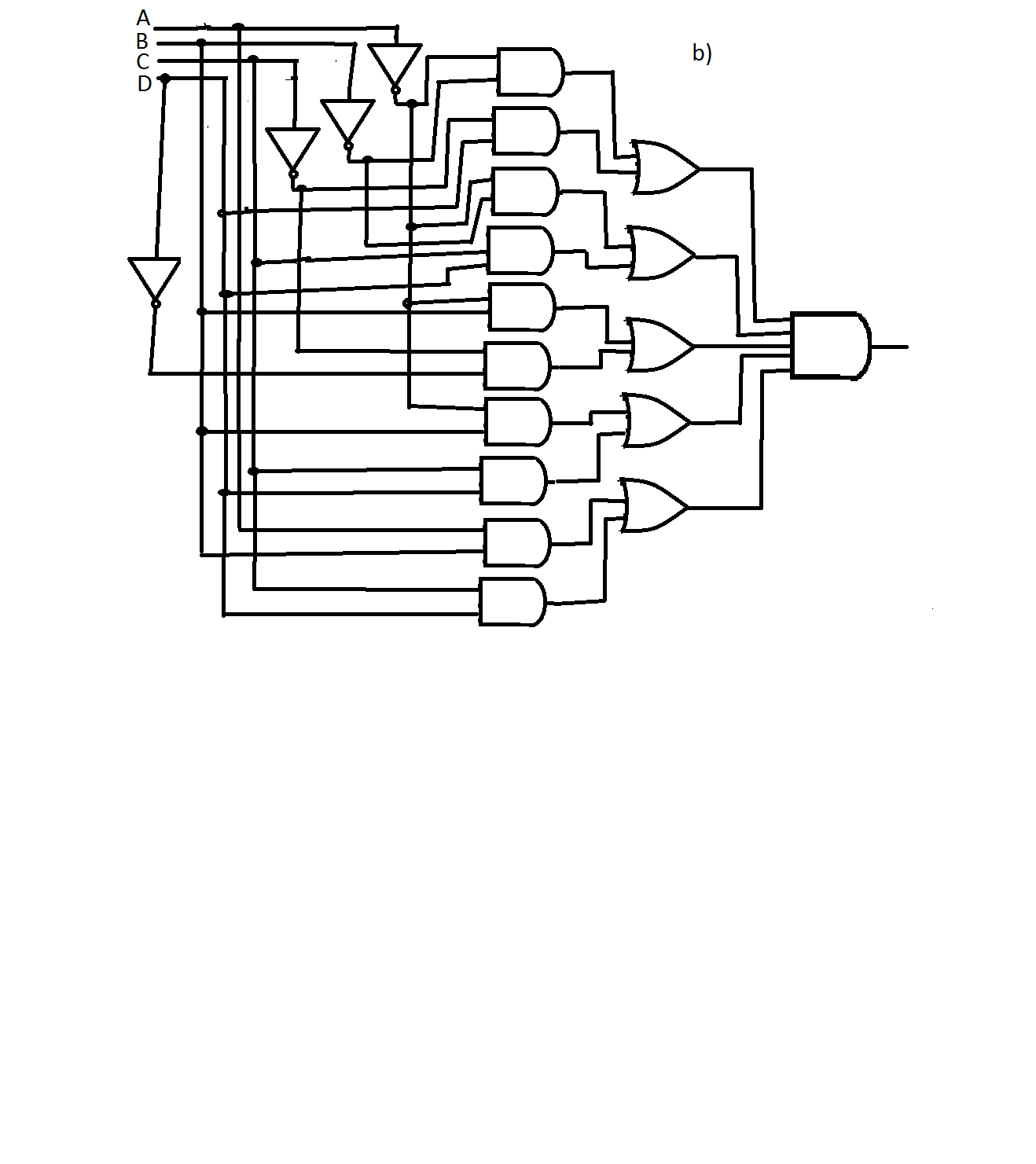

POS using NOR gates

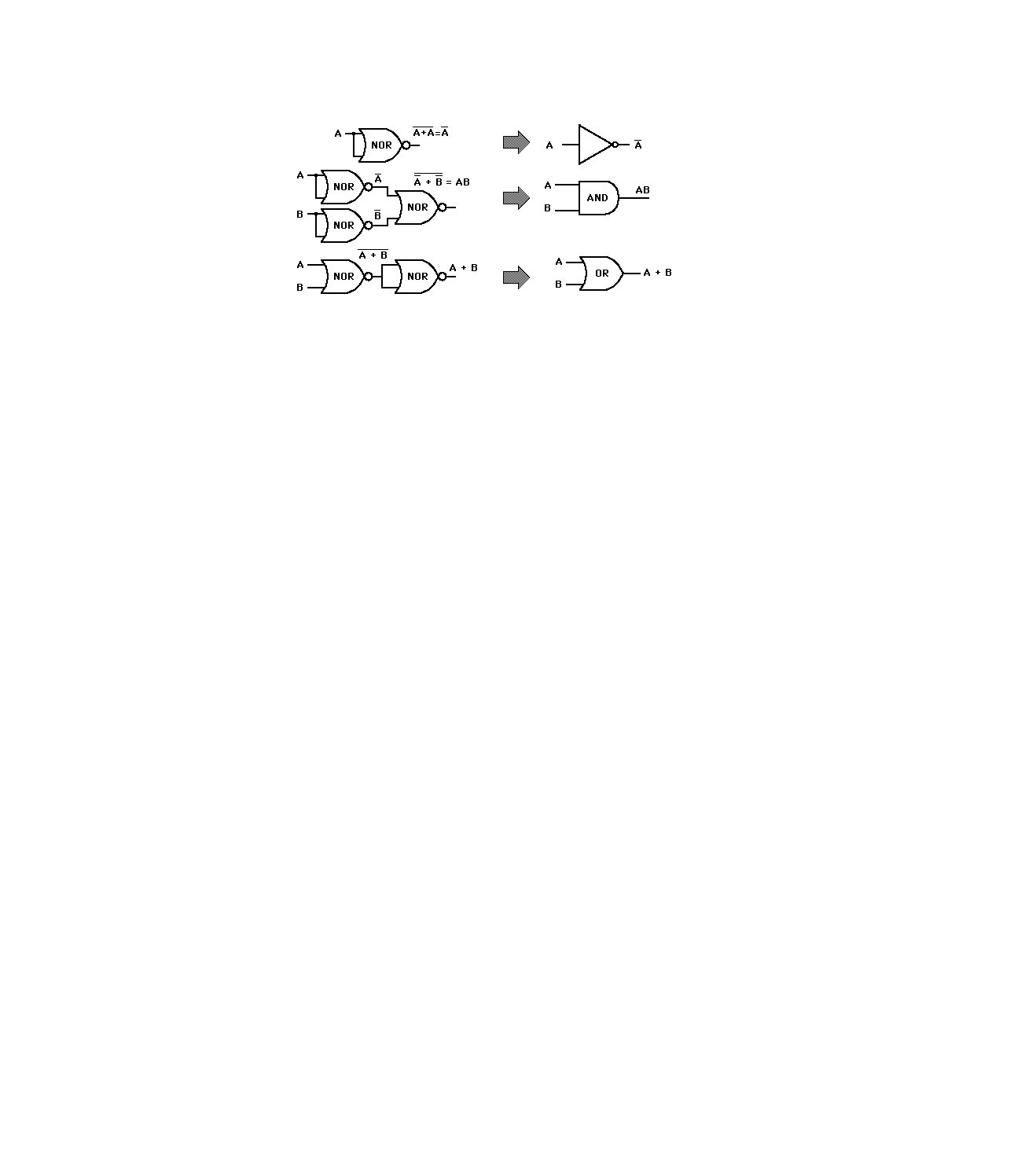

realize basic logic gates ( AND, OR, NOT) with NOR gate:

a)

b)